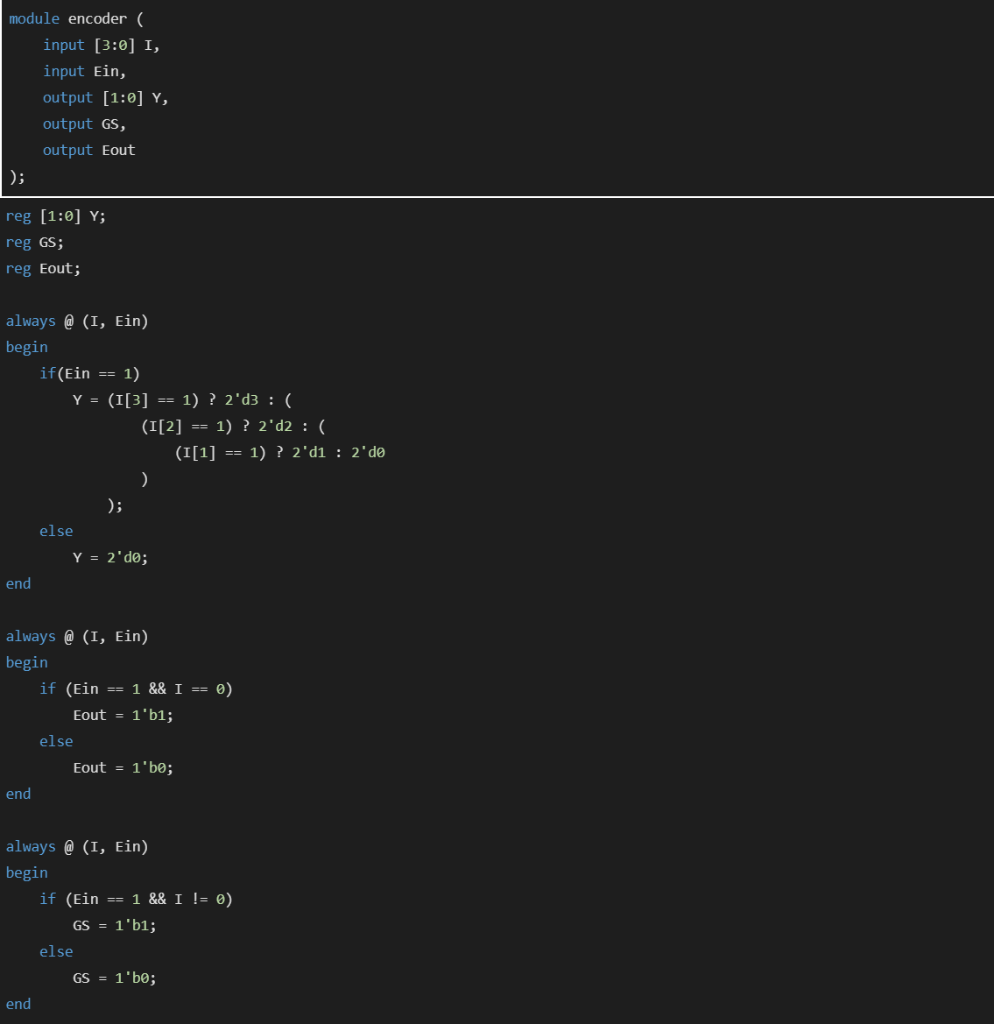

15+ pages 4 to 2 encoder verilog code with testbench 3mb. Verilog code for encoder and testbench. Input Y3 Y2 Y1 Y0. 0842 Unknown 11 comments Email This BlogThis. Read also code and understand more manual guide in 4 to 2 encoder verilog code with testbench Verilog Code for 4 to 2 Encoder Behavioral Modelling using Case Statement with Testbench Code Xilinx Code Gate level Modeling for 42 priority encoder.

Verilog Code for 1-2 DEMUX StructuralGate Level Modelling 1-2 DEMUX module DEMUX_1_to_2 input s input d output y0 output y1. Here we will be writing the VHDL code for a 42 encoder using the behavioral modeling style of architecture.

Verilog Code For Priority Encoder All Modeling Styles

| Title: Verilog Code For Priority Encoder All Modeling Styles |

| Format: PDF |

| Number of Pages: 319 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: May 2020 |

| File Size: 3mb |

| Read Verilog Code For Priority Encoder All Modeling Styles |

|

Verilog code for Mealy Machine.

A program written for testing the main design is called. At any time only one of these 4 inputs can be 1 in order to get the respective binary code at the output. Gate level Modeling for 42 priority encoder. Note that we declare outputs first followed by inputs as the built-in gates also follow the same pattern. Lets declare the input and output ports. Verilog code for 2-bit Magnitude Comparator.

Verilog Implementation Of 4 2 Encoder Test Bench

| Title: Verilog Implementation Of 4 2 Encoder Test Bench |

| Format: ePub Book |

| Number of Pages: 255 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: May 2018 |

| File Size: 810kb |

| Read Verilog Implementation Of 4 2 Encoder Test Bench |

|

Verilog Programming Series 4 To 2 Priority Encoder

| Title: Verilog Programming Series 4 To 2 Priority Encoder |

| Format: eBook |

| Number of Pages: 285 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: June 2019 |

| File Size: 2.3mb |

| Read Verilog Programming Series 4 To 2 Priority Encoder |

|

Vhdl Code For 4 To 2 Encoder

| Title: Vhdl Code For 4 To 2 Encoder |

| Format: eBook |

| Number of Pages: 314 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: March 2021 |

| File Size: 1.3mb |

| Read Vhdl Code For 4 To 2 Encoder |

|

Verilog Code For 2 To 4 Decoder In Modelsim With Testbench Verilog Tutorial

| Title: Verilog Code For 2 To 4 Decoder In Modelsim With Testbench Verilog Tutorial |

| Format: ePub Book |

| Number of Pages: 308 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: February 2021 |

| File Size: 800kb |

| Read Verilog Code For 2 To 4 Decoder In Modelsim With Testbench Verilog Tutorial |

|

Vhdl Code For 4 To 2 Encoder

| Title: Vhdl Code For 4 To 2 Encoder |

| Format: eBook |

| Number of Pages: 185 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: January 2018 |

| File Size: 3mb |

| Read Vhdl Code For 4 To 2 Encoder |

|

Verilog Code For Priority Encoder All Modeling Styles

| Title: Verilog Code For Priority Encoder All Modeling Styles |

| Format: ePub Book |

| Number of Pages: 173 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: December 2018 |

| File Size: 2.3mb |

| Read Verilog Code For Priority Encoder All Modeling Styles |

|

Vhdl Code For 4 To 2 Encoder

| Title: Vhdl Code For 4 To 2 Encoder |

| Format: eBook |

| Number of Pages: 221 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: January 2021 |

| File Size: 1.9mb |

| Read Vhdl Code For 4 To 2 Encoder |

|

3 Encoder Create A Verilog Description Of A 4 2 Chegg

| Title: 3 Encoder Create A Verilog Description Of A 4 2 Chegg |

| Format: eBook |

| Number of Pages: 159 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: August 2018 |

| File Size: 3mb |

| Read 3 Encoder Create A Verilog Description Of A 4 2 Chegg |

|

Verilog Code For Priority Encoder All Modeling Styles

| Title: Verilog Code For Priority Encoder All Modeling Styles |

| Format: PDF |

| Number of Pages: 235 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: December 2018 |

| File Size: 800kb |

| Read Verilog Code For Priority Encoder All Modeling Styles |

|

Verilog Code For Priority Encoder All Modeling Styles

| Title: Verilog Code For Priority Encoder All Modeling Styles |

| Format: PDF |

| Number of Pages: 200 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: December 2019 |

| File Size: 810kb |

| Read Verilog Code For Priority Encoder All Modeling Styles |

|

Vhdl Code For 4 To 2 Encoder

| Title: Vhdl Code For 4 To 2 Encoder |

| Format: ePub Book |

| Number of Pages: 181 pages 4 To 2 Encoder Verilog Code With Testbench |

| Publication Date: June 2020 |

| File Size: 1.35mb |

| Read Vhdl Code For 4 To 2 Encoder |

|

Verilog code for 2-bit Magnitude Comparator. As any Verilog code we start by declaring the module and terminal ports. First we have to test whether the code is working correctly in functional level or simulation level.

Here is all you need to know about 4 to 2 encoder verilog code with testbench Now we can declare the intermediate signals. First we have to test whether the code is working correctly in functional level or simulation level. You will need four inverters NOT gates four 5-input AND gates well they dont come as 5-input devices so either use cascaded 2-input or 3-input or four 8-input AND gates and a 4-input OR gate. Verilog code for priority encoder all modeling styles vhdl code for 4 to 2 encoder vhdl code for 4 to 2 encoder verilog code for priority encoder all modeling styles verilog code for 2 to 4 decoder in modelsim with testbench verilog tutorial verilog code for priority encoder all modeling styles 4 To 16 Decoder Using 2 To 4 Decoder Verilog Code.